DSA时代,如何快速设计出一款特定领域的SoC,完成复杂的软件栈开发和硬件验证,并快速推向市场,是各类AI芯片公司追求的目标,也是目前大家遇到的最大挑战。

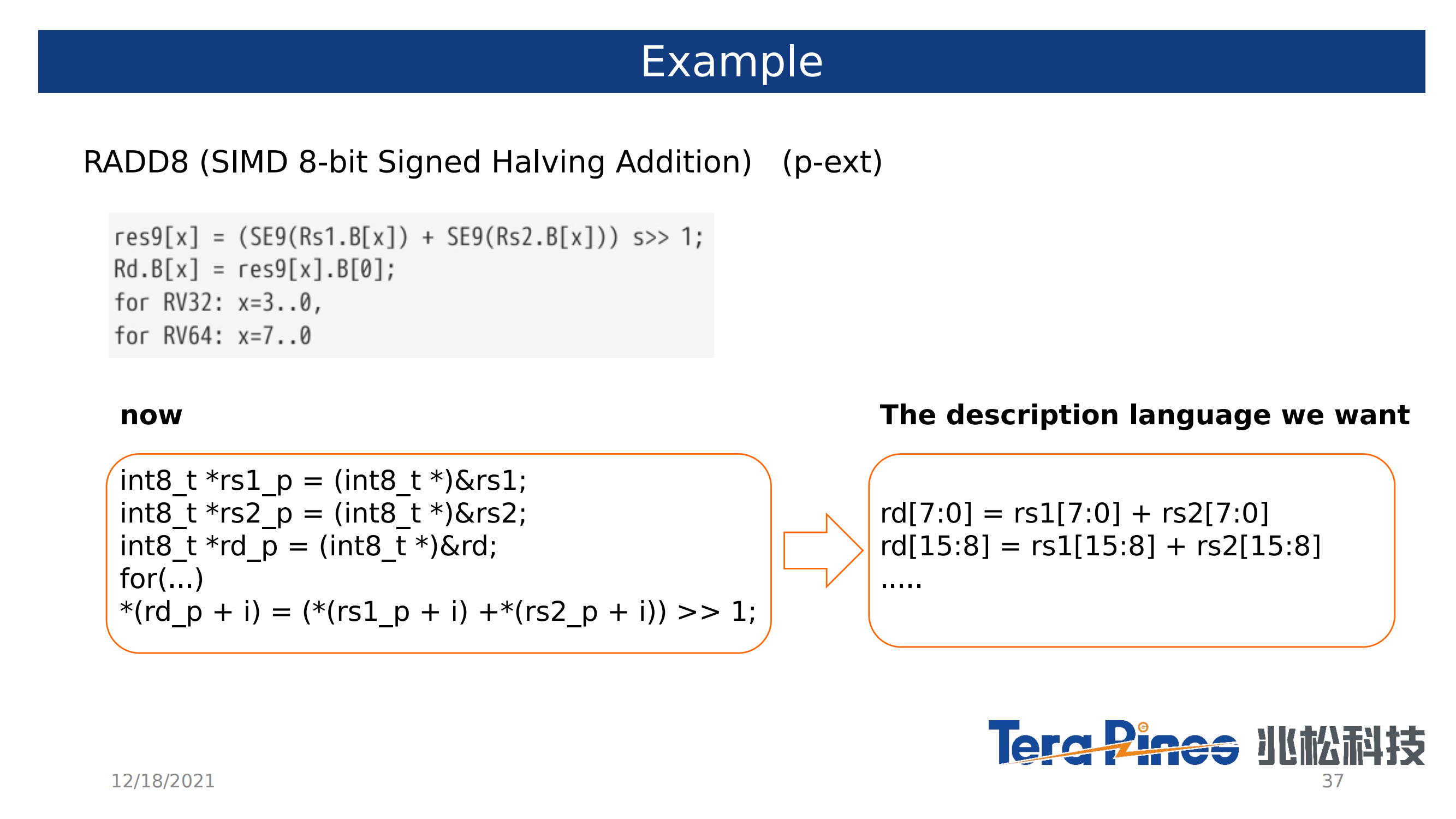

复杂SoC芯片设计面临几大问题:1. 如何在设计初期,定量的评估SoC各个模块的参数,ISA定制化等,让加速器可以高效运行的情况下,最大程度节省SoC的面积和功耗;2. 复杂SoC的软件栈研发是一个大工程,目前市场上并没有什么通用的建模工具,来帮助SoC设计者快速搭建虚拟模型,虚拟模型除了可以用来做定性/定量分析之外,还可以大幅加快SoC上的软件开发,调优,以及连续整合测试,发布等;3. 由于异构SoC大多应用在人工智能领域,如果使用传统的基于CPU的仿真器来仿真异构SoC上面的加速器负载,结果必然是仿真速度非常不理想,影响开发进度;4. 由于FPGA单颗芯片的LUT有限,单颗FPGA芯片无法放下整个SoC的时候,虽然可以将SoC按模块切割到多块FPGA板子上进行仿真,但是这又会带来其他问题,比如编译速度以及仿真速度远远比不上单块FPGA。

以上列举的一些常见问题其实归根结底是时间以及成本的问题。当前需要寻找新的方案来降低各芯片公司的研发成本,加速产品研发速率。我们兆松科技成立的目标之一,就是为了帮助大家解决这些难题。

今天,我们给大家带来的是兆松科技研发的工具箱中的一款工具: zemu/zvboard – A co-design platform.

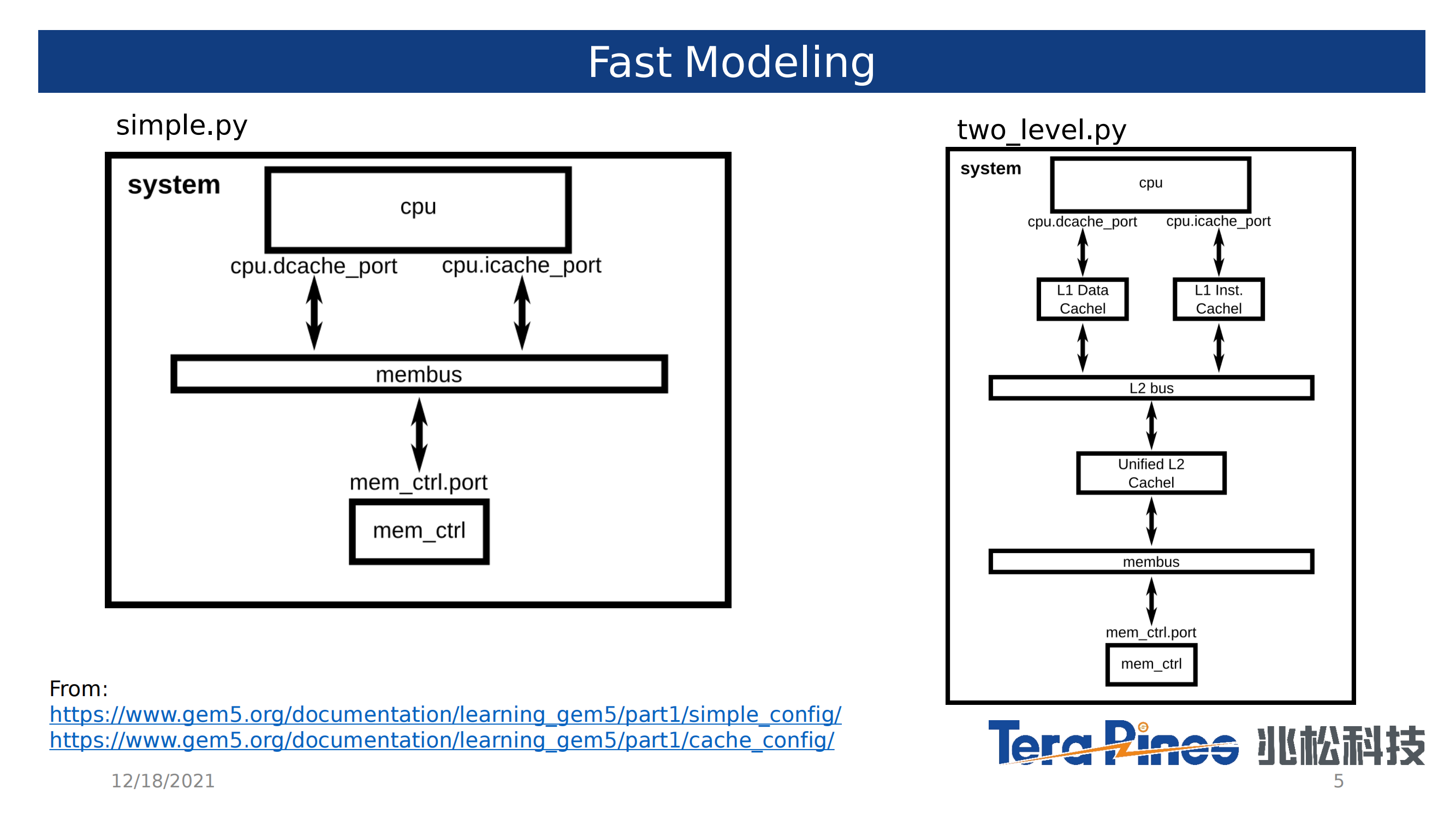

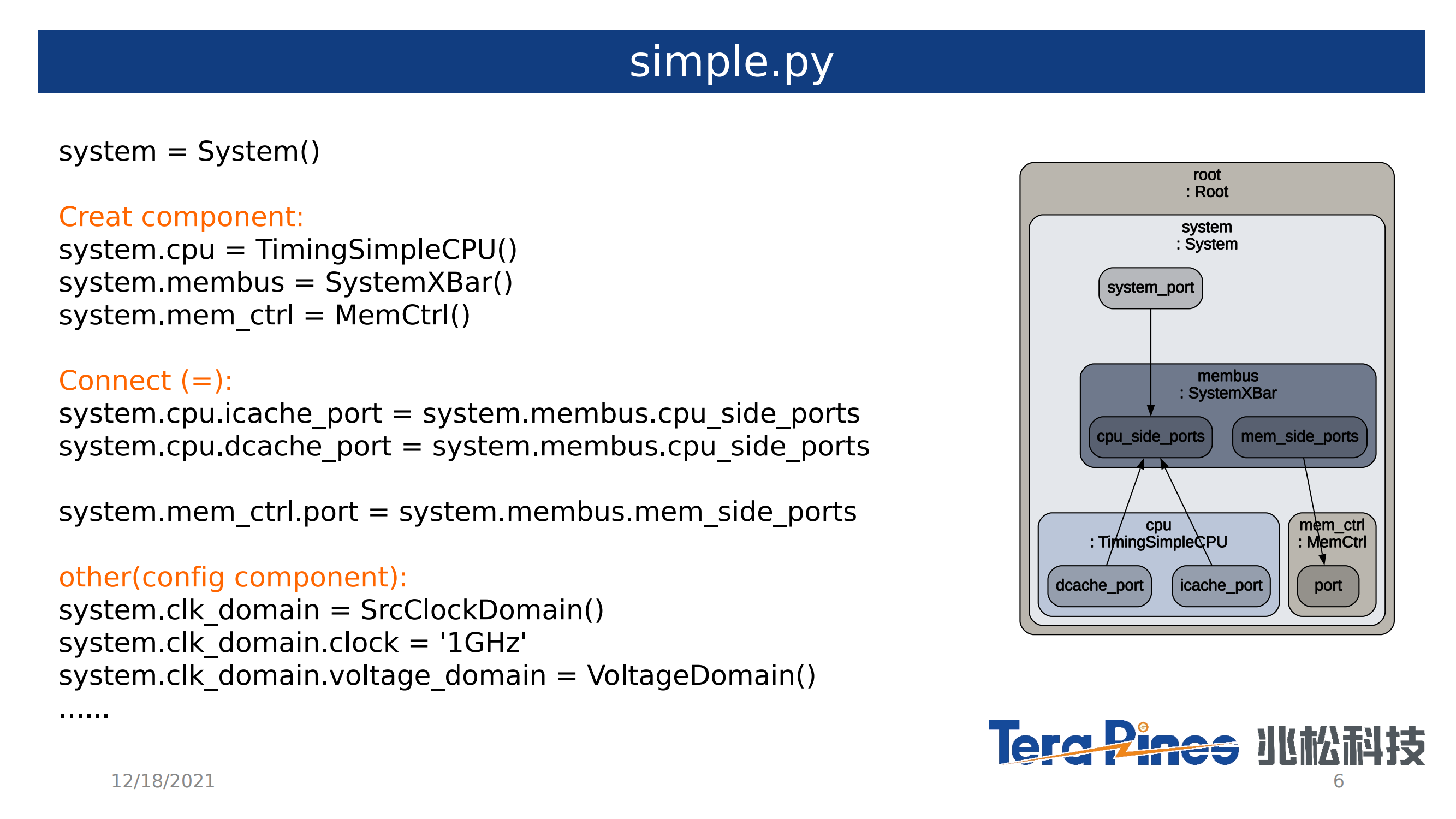

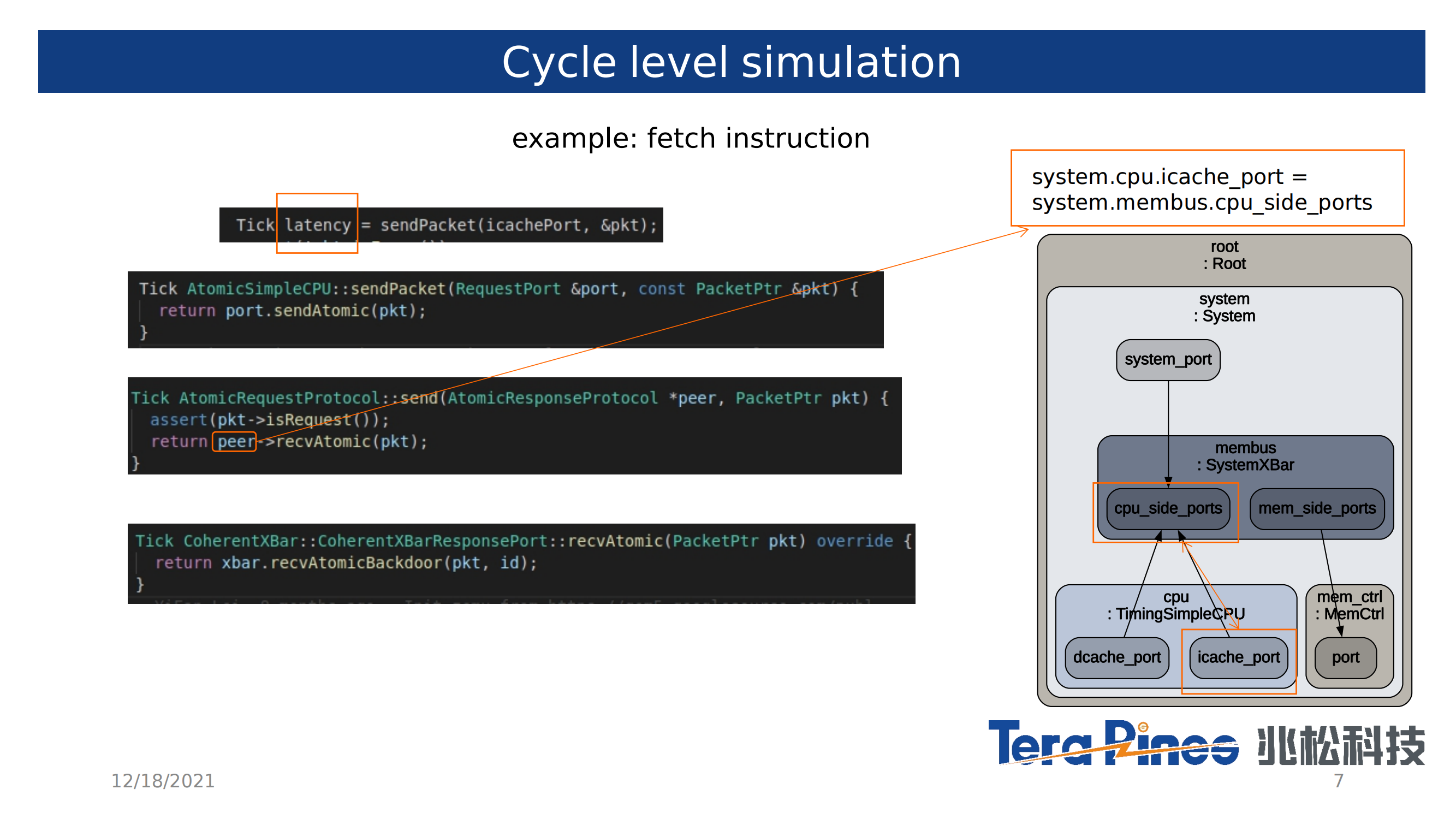

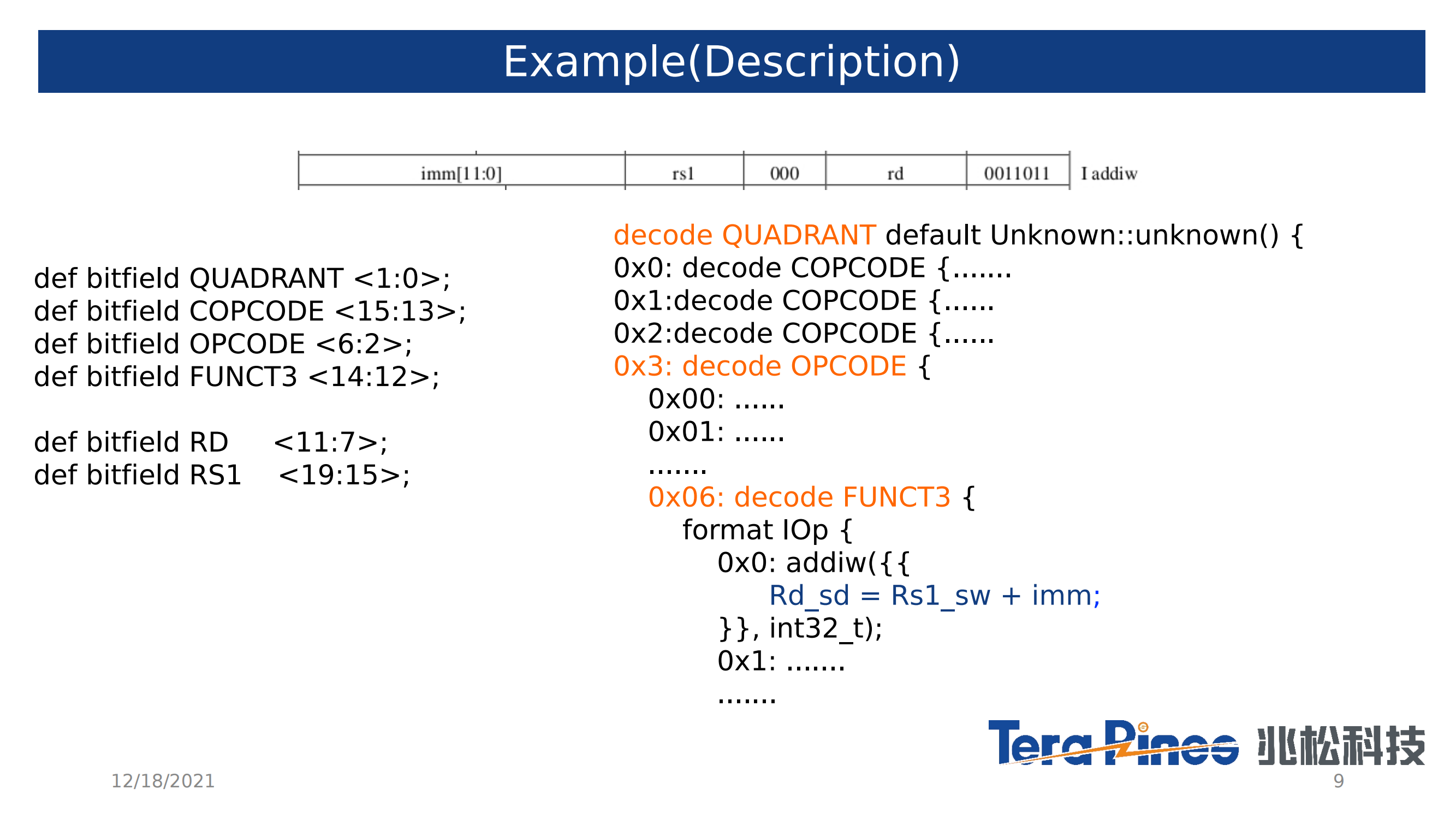

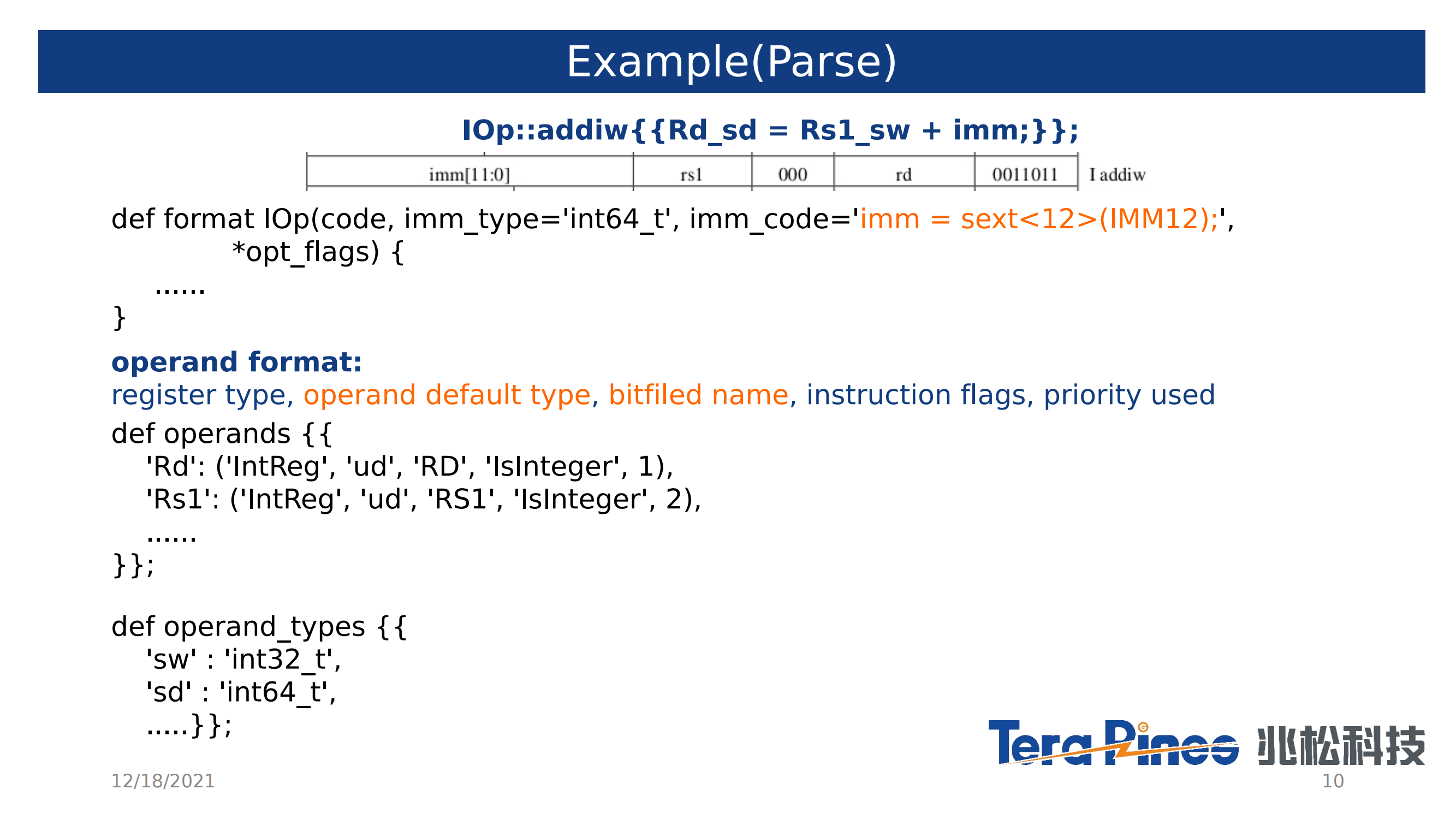

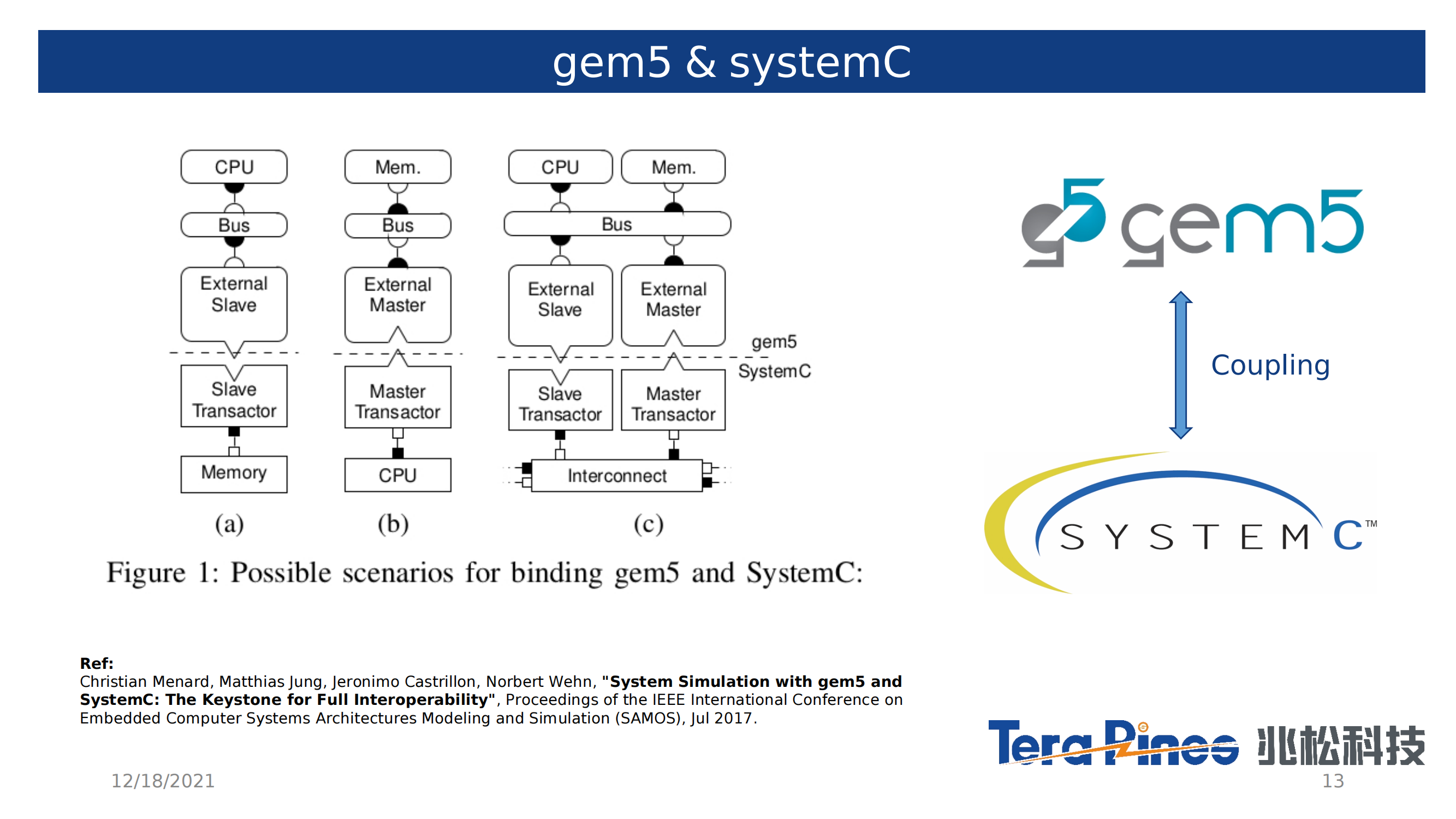

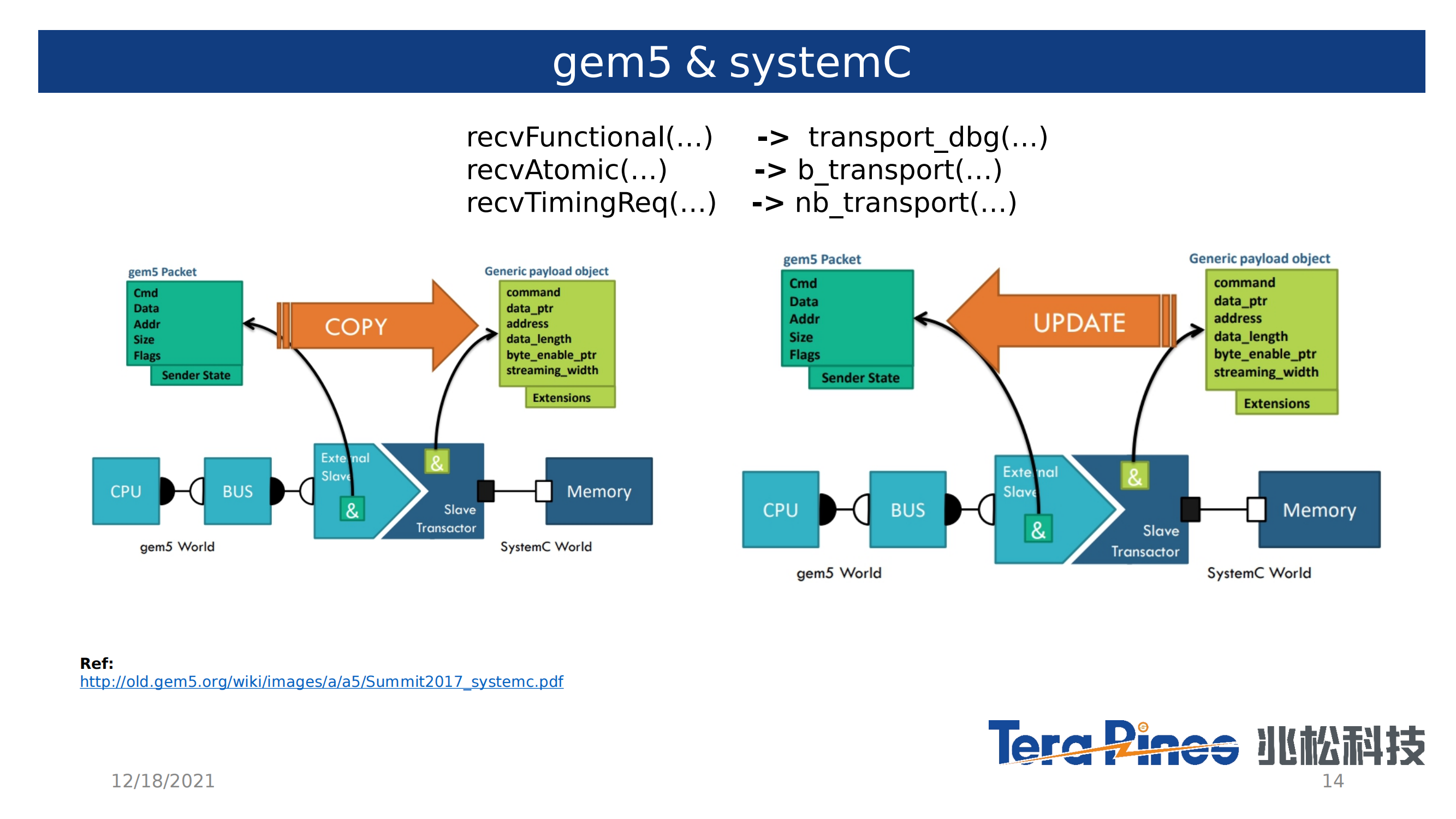

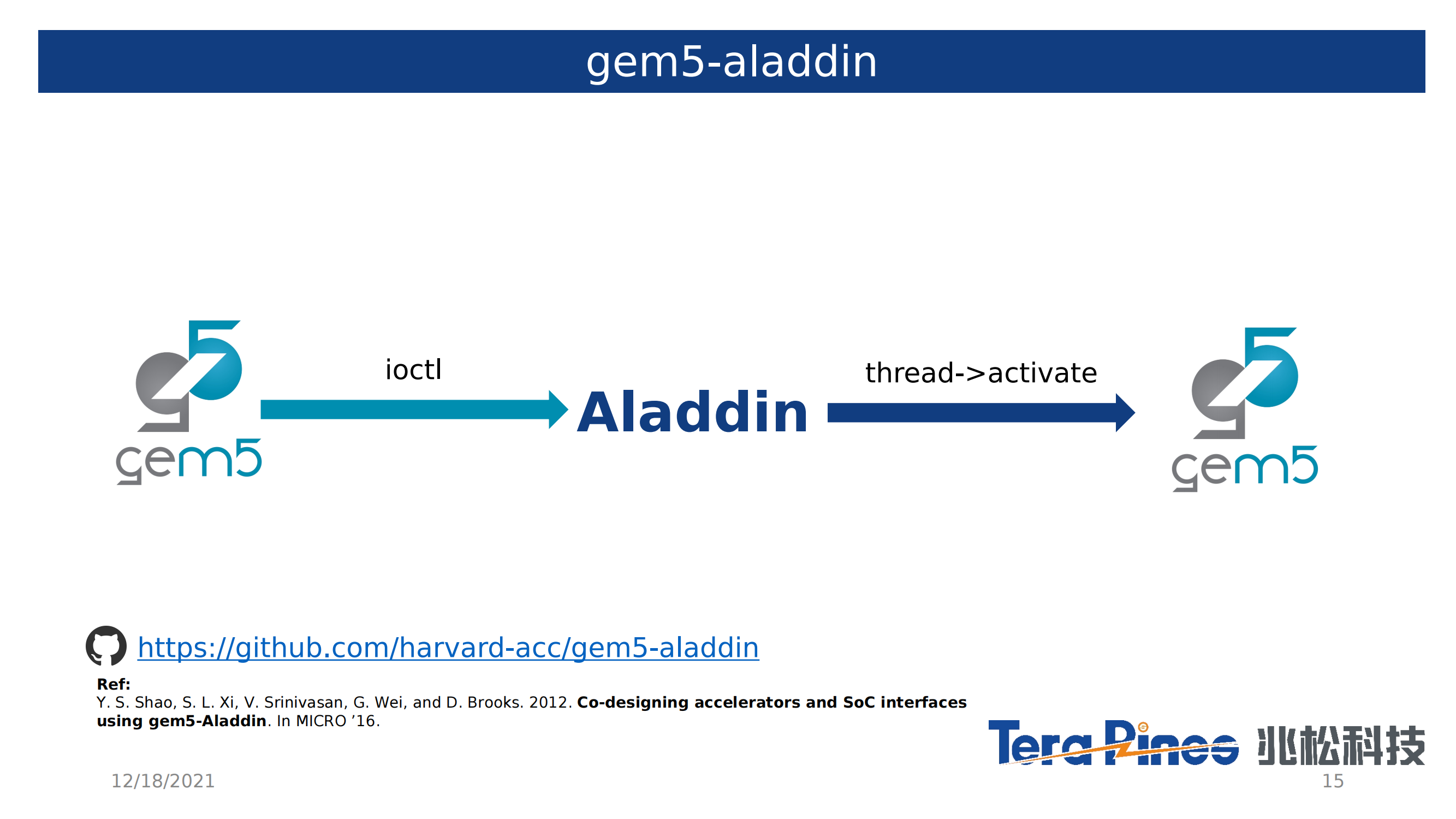

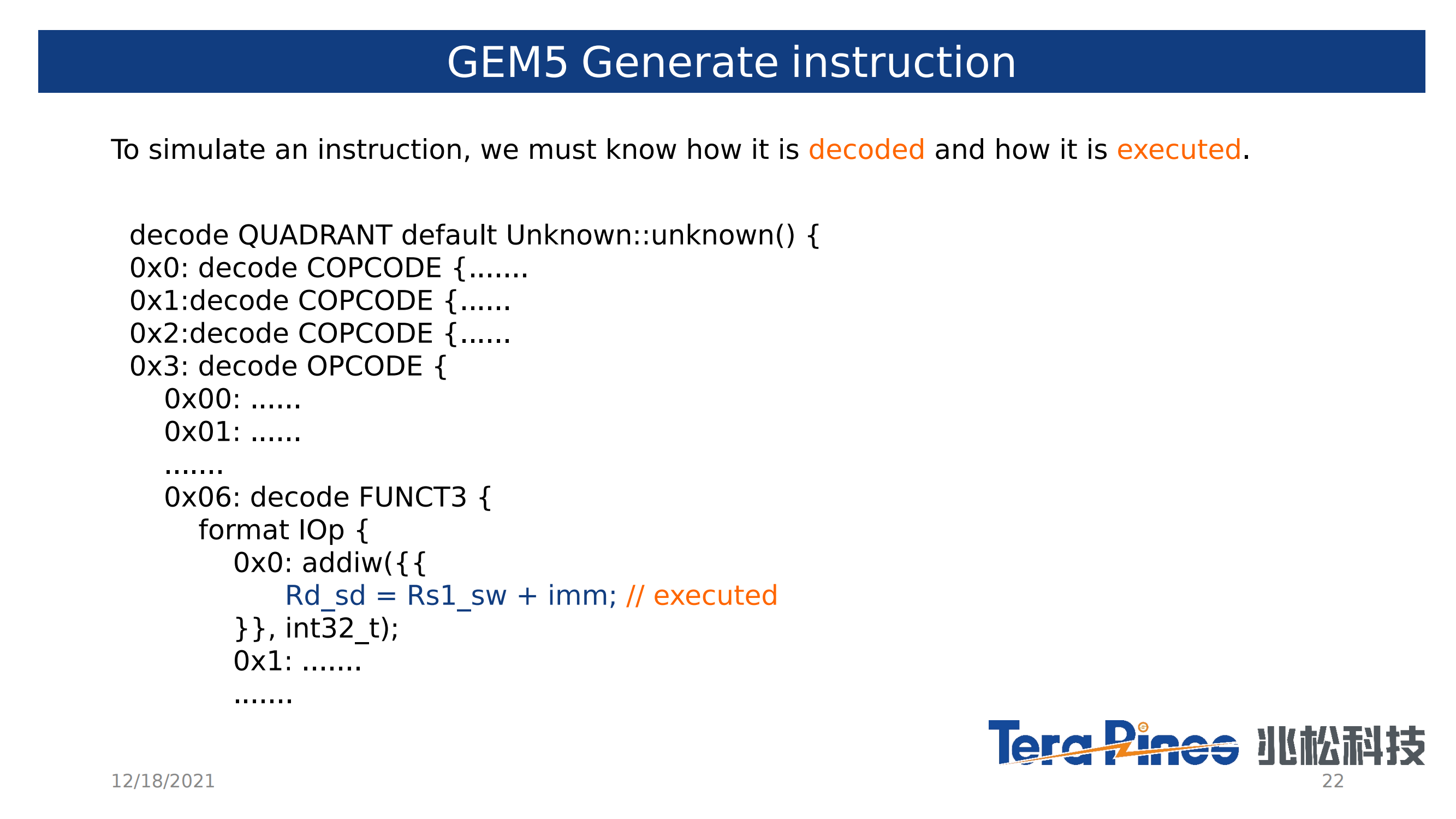

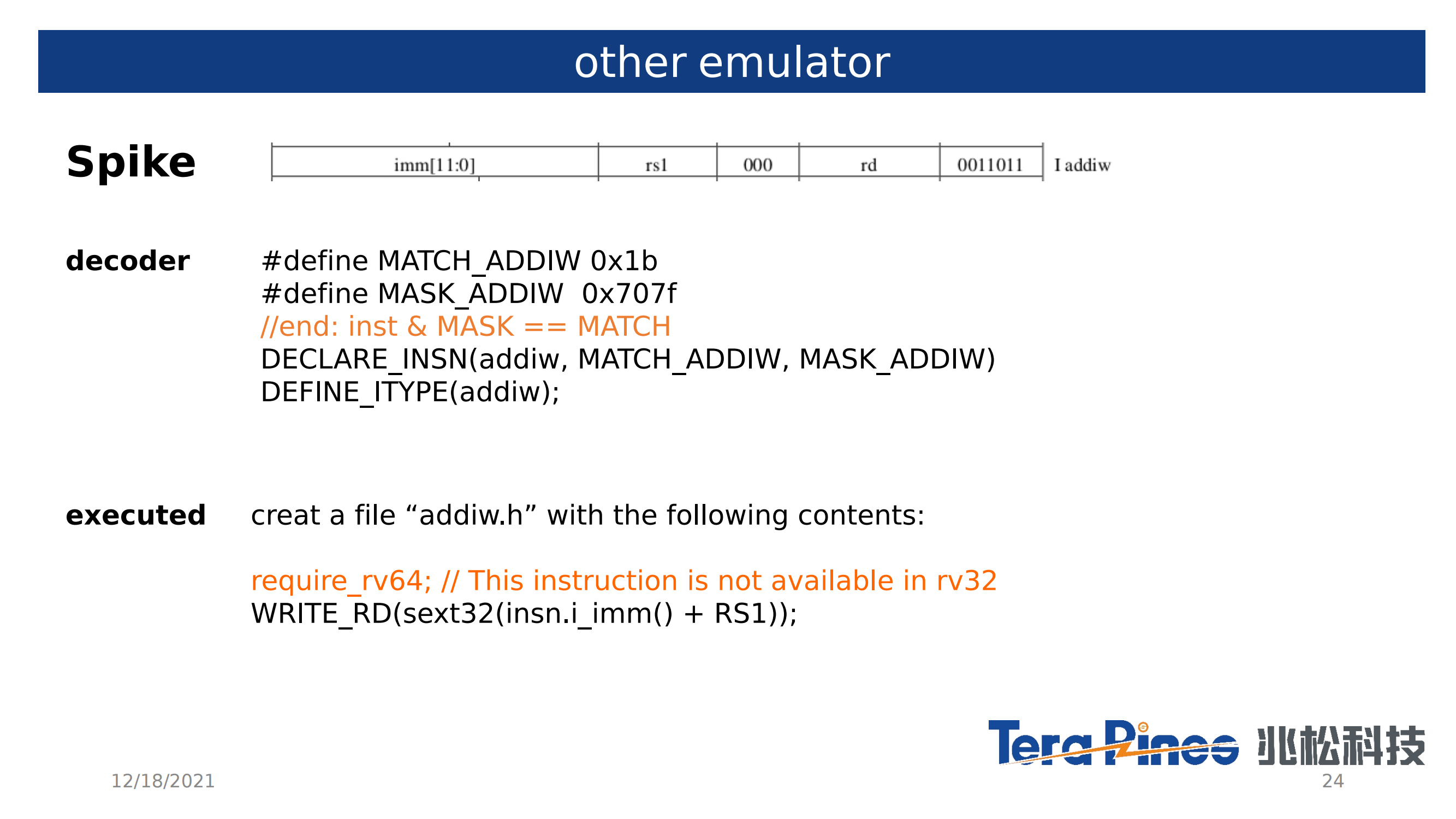

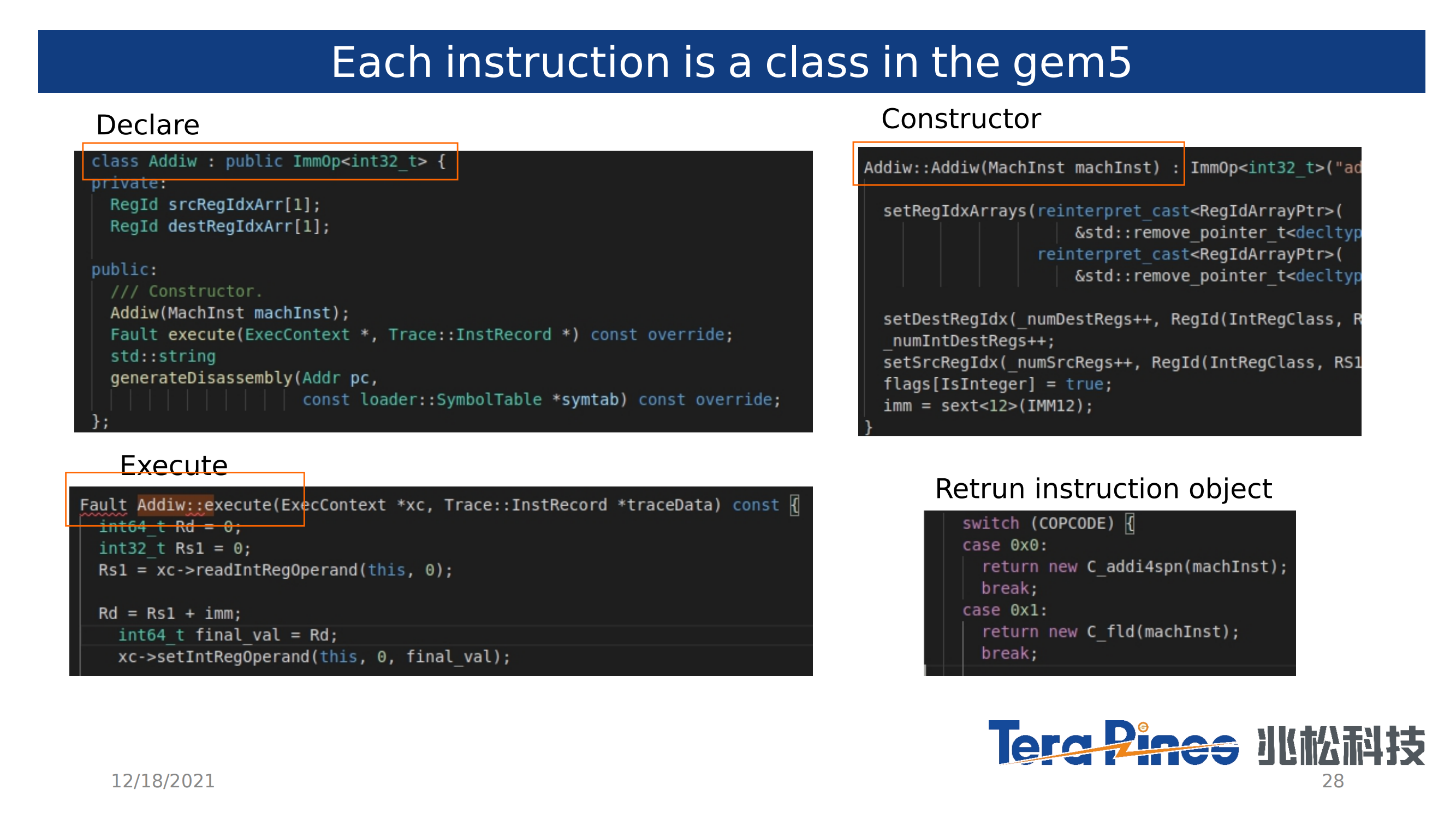

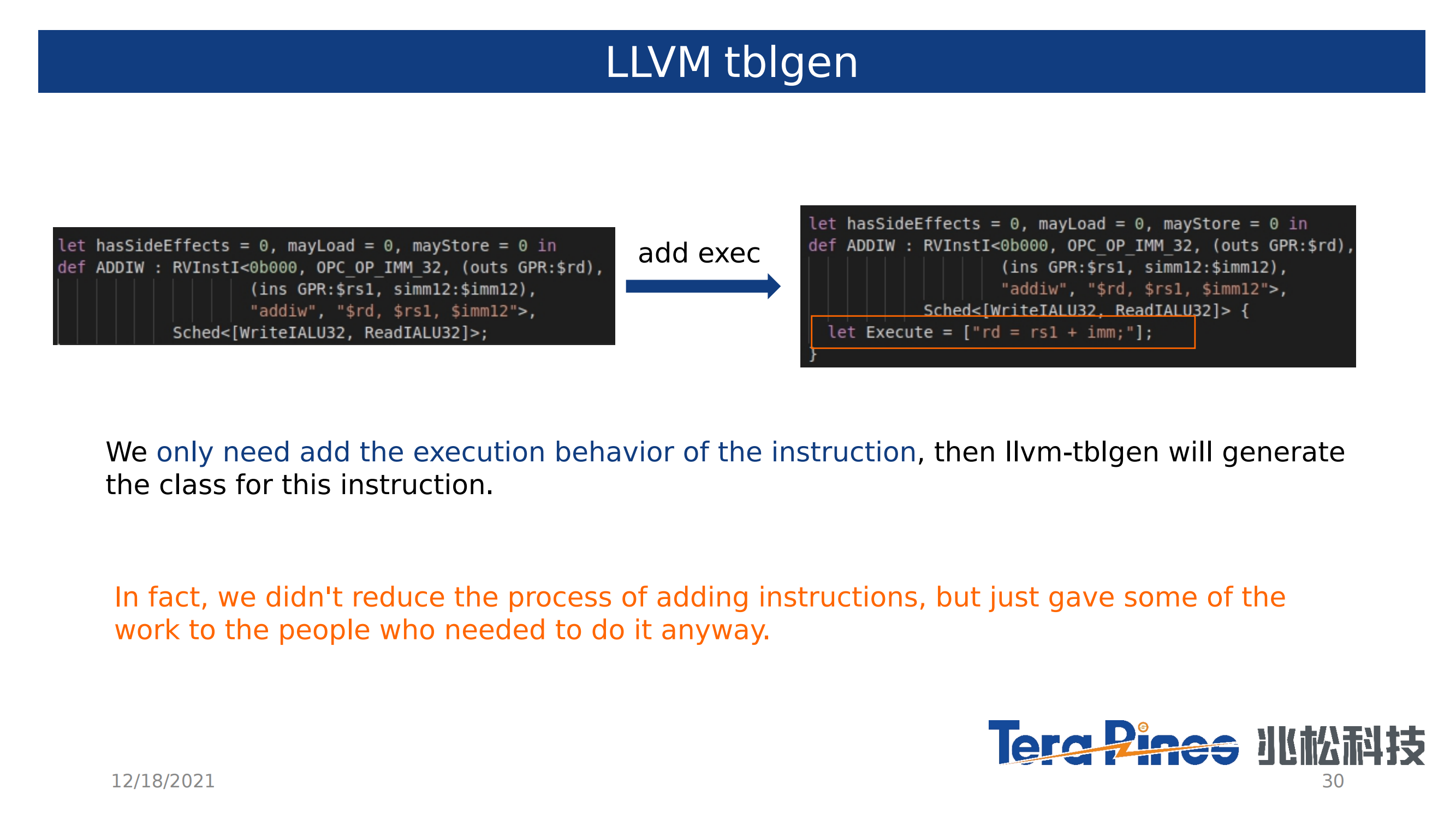

zemu是我们目前正在研发的一款仿真器工具,zemu选择使用当前在计算机体系结构研究中最受欢迎的仿真器之一的gem5作为基石,与当前编译器中的王者llvm完成一个深度融合,极大的简化了开发流程,降低了开发难度,从而大大的加快了开发速度。众所周知,gem5快速建模的特性绝对是一流的,同时他还有着cycle accurate仿真以及功耗仿真的底子,这对于SoC的性能评估无疑是十分必要的。其次,gem5还提供了十分方便的接口,简化了实现co-design和co-simulation的难度。而zemu正是在这样一个强大的基础之上进行了进一步的优化使之更加贴合当前需求。不过由于对zemu的定位需要其有高度自由的可配置性(至少要能支持所有同构/异构SoC模型的搭建),如果同时需要及其苛刻的精确度的话,用户在使用时需要配置大量的参数,假如全都使用文本操作,则极有可能会造成多数用户体验的下降,而我们的zvboard工具正是为了解决快速建模的问题。

zvboard是一款图形界面的ESL(Electronic System Level design)工具,为了提高使用体验和建模速度,我们使用可拖拽图形化的界面,提供丰富的C /Verilog/Chisel model的IP,方便使用者不使用任何编程语言,就可以快速搭建起一个SoC的虚拟模型。Zemu可以对模型进行快速或者时钟精准的仿真(使用时钟精准模型可以方便硬件设计工程师进行硬件设计初期的定量评估,使用快速模型可以帮助软件开发工程师在硬件还没有成型时进行软件开发)。

接下来我们将沿着这个方向继续前进,进一步加快zemu的仿真速度(比如使用CPU多线程,GPU加速某些模块的仿真),提高仿真精度,持续改进zvboard的用户体验,逐步在zemu当中实现全自动生成可综合的SoCRTL以及C/C++编程接口的功能。

文后B站视频和PPT是兆松团队的雷依钒参加OSDT 2021所分享的关于zemu(gem5)的详细内容。

OSDTConf2021视频:

OSDTConf2021演示文稿: